2025.07.12

はんだ付けにおける濡れ不良について

フロー&リフローはんだ付けにおいて、ブリッジや未はんだ、ブローホールなどの不良に次いで比較的多発している「濡れ不良について」これまでの経験事例を踏まえて要因と対策を説明します。

はんだ付けは、加熱~濡れ~拡散~合金化のプロセスで行われますが、はんだ付けの良し悪しは「接合材界面の濡れ性」に大きく依存しますのではんだ付け部の表面状態(酸化程度、めっき種&厚み、合金層)が重要になります。以下に不具合の事例と対策を説明します。

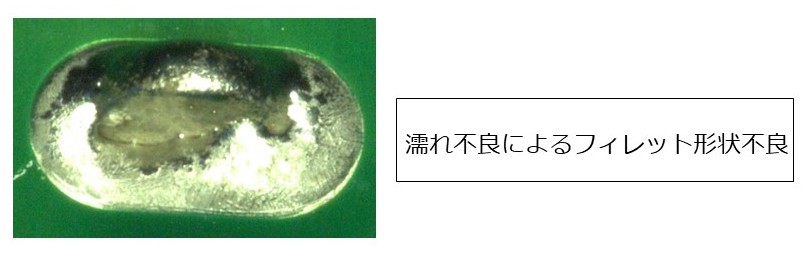

①電子部品リードの濡れ不良:リン青銅端子材質などでSnめっき皮膜が薄く長期保存により酸化劣化し不濡れとなる場合があります。主にリード部にはんだ不濡れが生じてフィレット形成不良になります。

※対策:納入仕様書にて部品リードのめっき種&厚み、保存条件などを確認して管理を徹底する。

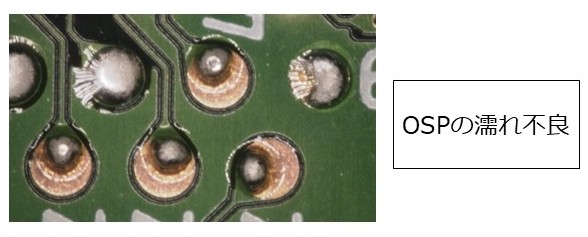

②OSP基板の濡れ不良:ペースト印刷を失敗して溶剤で拭き取り後、OSP被膜が除去され銅箔が酸化して再印刷リフロー時に濡れ不良となる場合があります。

※対策:OSP基板やロジン系プリフラックス処理基板の場合には溶剤拭き取り後の使用不可とする。なお、はんだレベラー基板では問題ありません。

③はんだレベラー基板の濡れ不良(リフロー、両面リフロー+フロー)

はんだレベラー基板はパッド上のはんだ厚みが数~50μmとバラツキが大きいことから近年の高密度基板では、ホットエアー圧を高めてはんだ厚みを薄くする傾向があり、リフロー時の濡れ不良やリフロー後のフローはんだ付けにてTH濡れ上がり不良やランドの濡れ不良が発生しやすくなっています。

※対策:レベラー基板の保存条件管理を徹底する。場合によってはOSP処理やAuめっき処理に変更する。レベラー処理条件を見直す(特にホットエアー圧)、活性力の高めのペーストやフラックスを使用する。

④QFN-LSIの端子の濡れ不良

QFNパッケージの場合には製造の最終段階にてリードフレームを切断するのでQFN端子面積のほとんどが露出してしまい酸化しやすくなり、リフロー後の濡れ上がり不良となり、小基板では基板分割時のストレスによりQFN端子接合部にクラックが入りやすくなります。

※対策:活性力の高いペーストを使用する。基板分割ストレスには要注意

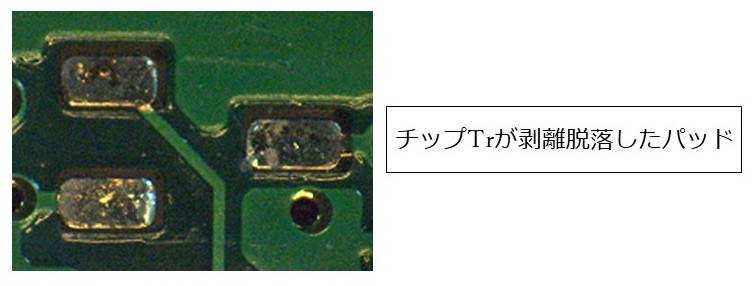

⑤Auめっきパッドの濡れ不良

リフローはんだ付け後には問題ないように見えるが、製品として組み込んでから使用時のちょっとした衝撃などによりチップ部品が剥離&落下する場合があります。原因は、一見、良くはんだが付いている様には見えるが金めっき基板特有な接合不良です。金めっき基板では表面の金被膜がはんだ付け時にはんだ中へ拡散消失し、下地のNiめっき層とはんだが合金層を形成し接合が完了します。基板製造プロセス(Ni-Auめっき)において何らかの異常(Ni被膜の汚れ、酸化など)が発生するとはんだ付け時に良好な接合が出来なくなります。パッド接合面が黒く変質してはんだが弾く状態になり「ブラックパッド」と言われる不良です。

※対策:Ni-Auめっき工程の見直し改善

関連記事こちらの記事も合わせてどうぞ。

2026.02.14

コラム記事(No.56) 「チップ型電解コンデンサーの開発実用化」について

2026.01.10

コラム記事(No.56) 「基板設計とはんだ付け品質」について

2025.11.07